With the increasing of the system complexity, the needs of system level design automation becomes more and more urgent. The maturity of high-level synthesis pushes the desgin abstraction from register-transfer level (RTL) to software programming language like C/C++. However, the state-of-art high-level synthesis tools mainly focus on the module-level optimization and implementation such as the scheduling and binding of operators and controls in a certain C/C++ function. System-level optimizations such as module selection and duplication, communication and memory optimization and system integration still need a great amount of manual effort to achieve desired quality of result and the correctness guaranteed system. The goal of this project is to establish a complete and automated end-to-end system design and optimization flow.

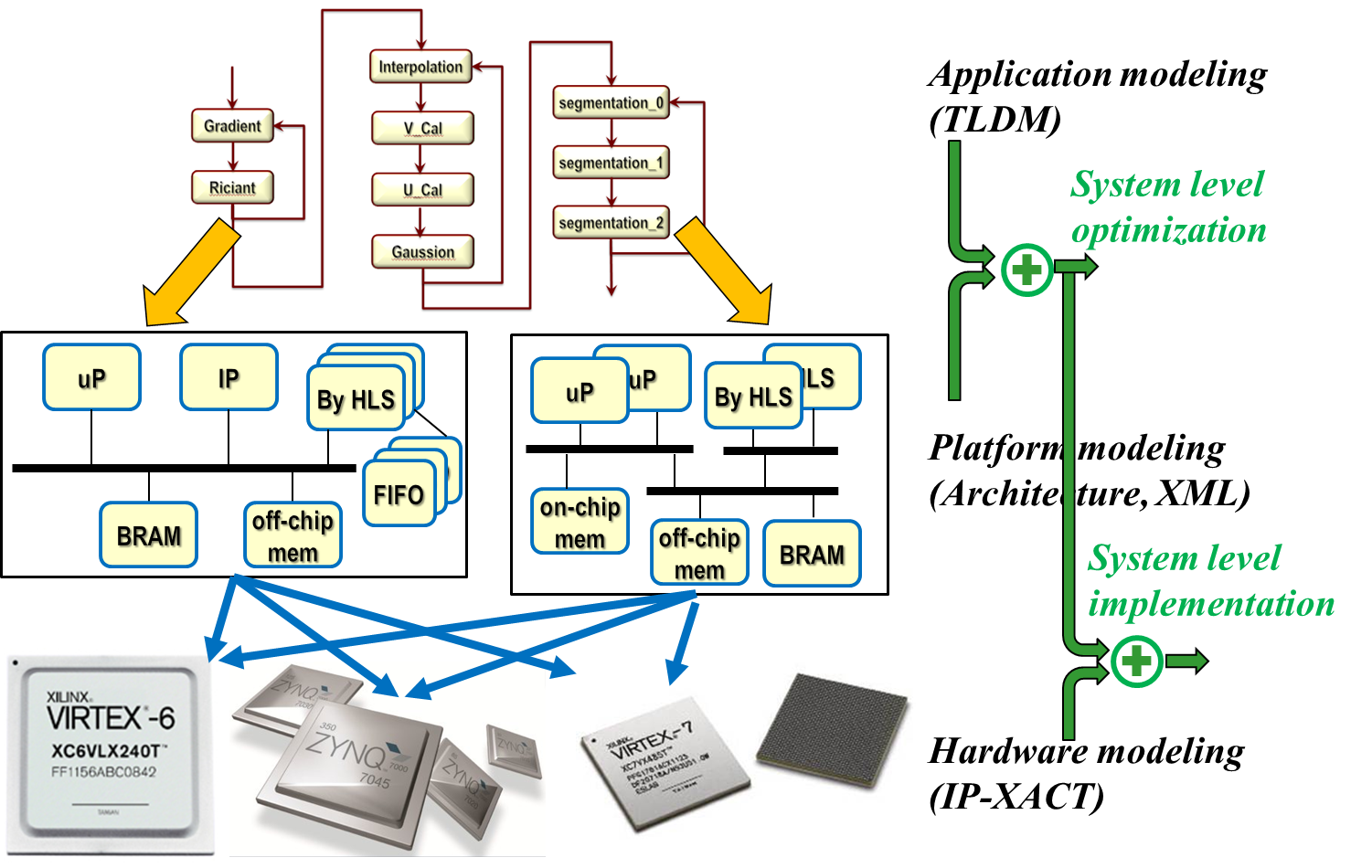

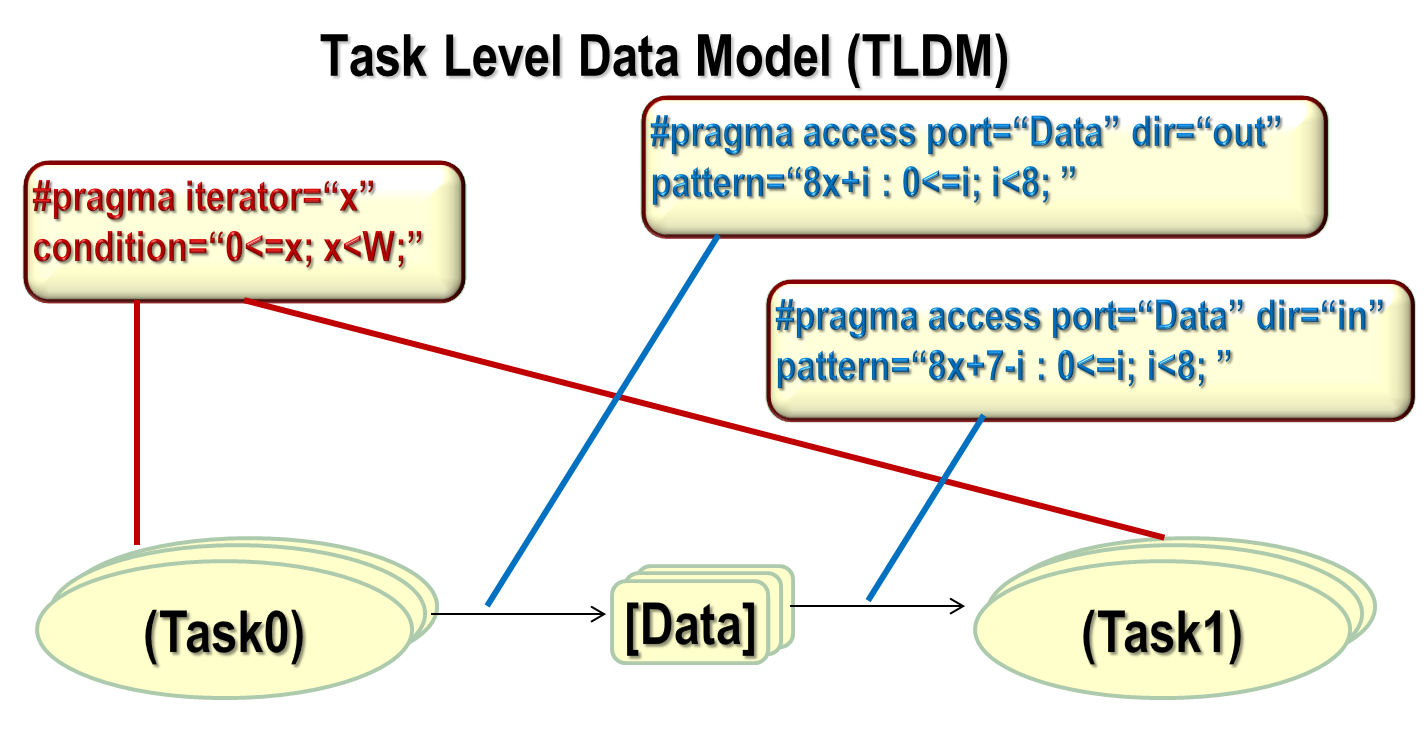

To increase the design efficiency for the complex systems, system-level optimizations needs high design abstraction. From application behavior perspective, the project takes the high-level program as the input, which includes C/C++, and openCL. The module-level behavior is specified as functions in sequential language, while the system-level information is explictly specified using our task level data model (TLDM), TLDM defines the iteration domain of the repeated tasks, and the regular data access patterns of each task instances in a concise way. This abstraction makes the complex module details transparent to the system level design, while providing a way to enable various efficient polyhedral-based system optimizations. From hardware platform perspective, the architecture of the system is modeled as parametric components in the XML files. The implementation details of the hardware components are abstracted out, and the system level mapping from TLDM to the architecture templates are greatly simplified. The abstraction of platform model helps to separate the platform independent system optimization and platform dependent system implementation.

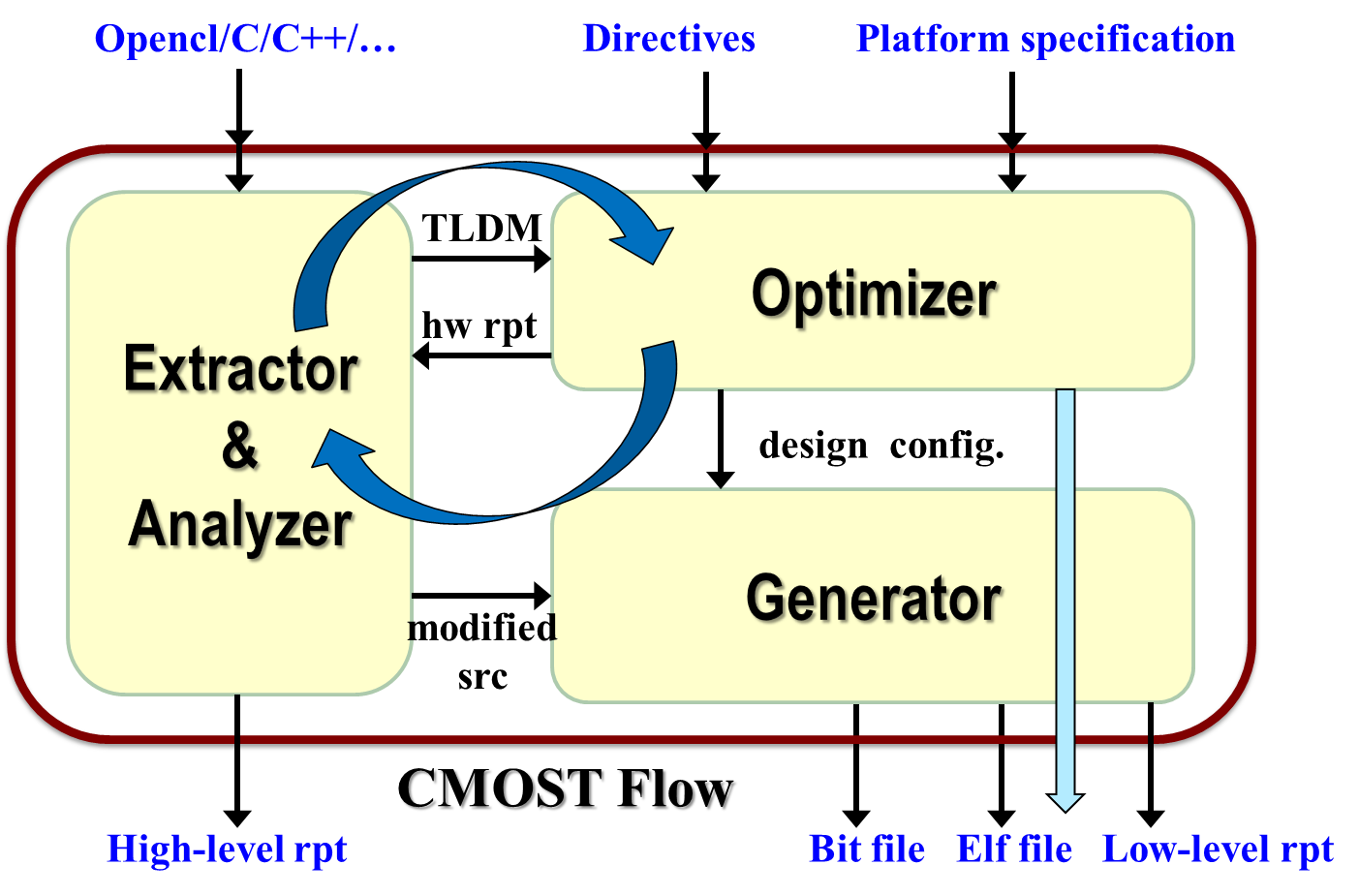

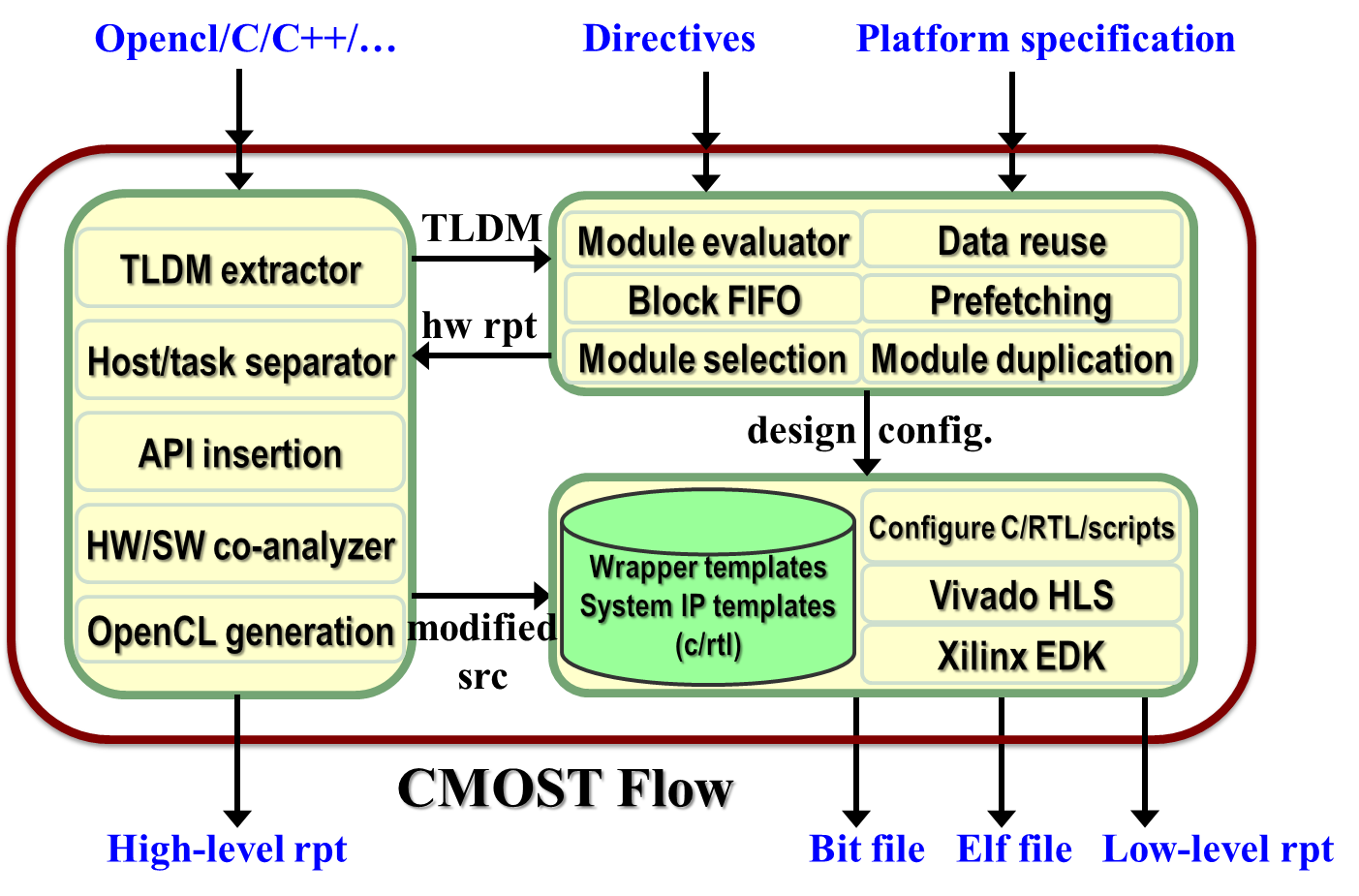

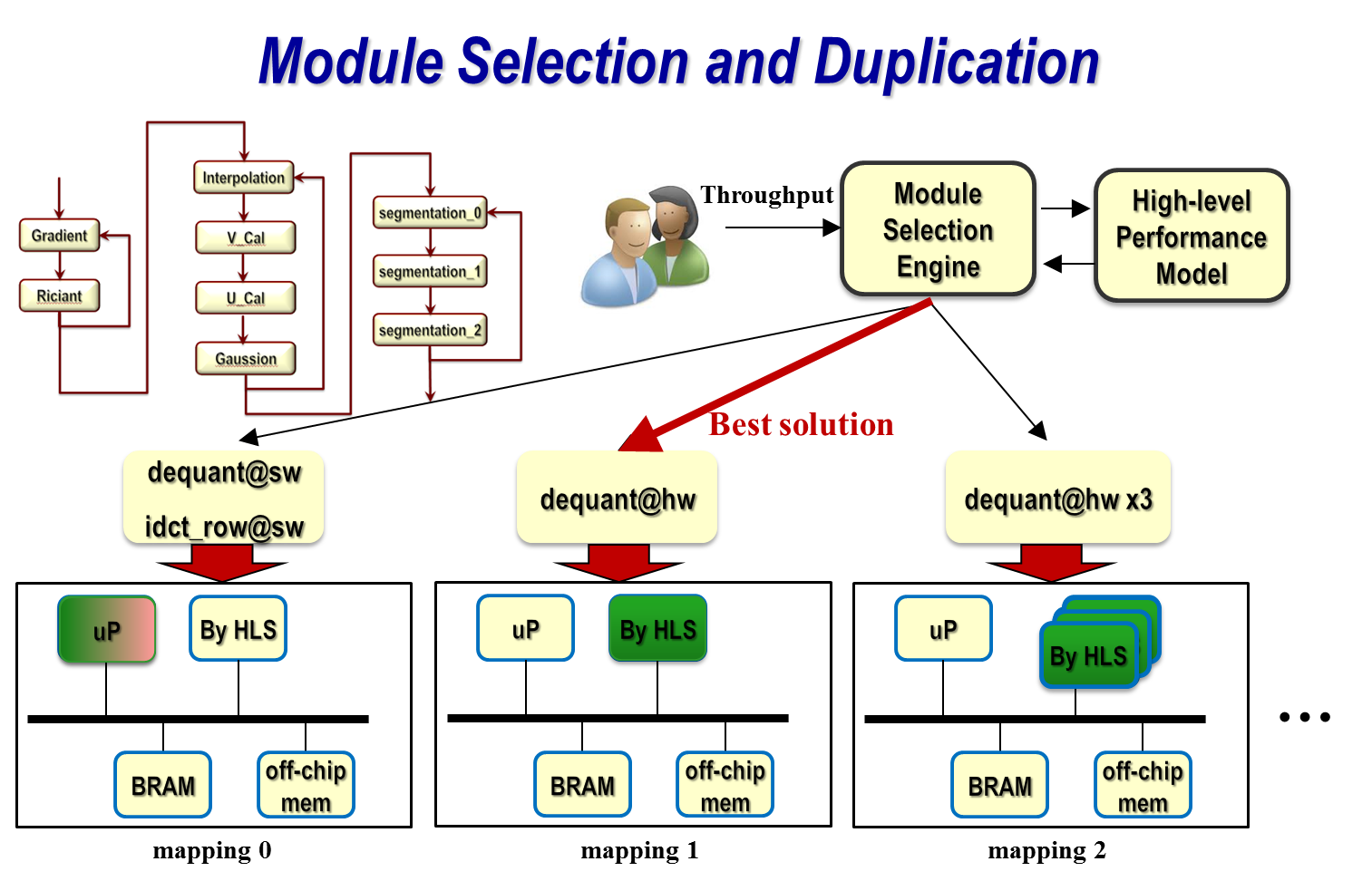

System level design needs to consider the multiple designs aspects including configuration, mapping, optimization, scheduling, and transformation (CMOST). Configurability, provided by our configurable source code format, gives a uniform way to manage reusable design template in different types of source coding including C, RTL or even scripts. Scheduling and mapping are optimized for each task instance according to the system level information specifed in TLDM, and module selection and duplication are intelligently done by considering the tradeoffs between system metrics. A set of pratical platform dependent optimizations, such as data reuse, access prefetching, buffer size reduction, are performed by automated high-level transformations on TLDM specification. In the CMOST design flow, an automated end-to-end design path is established which contains the extractor which derives the TLDM information from user source code, an optimizer which performs system level optimizations, and a generator to create the whole executable system on FPGA.

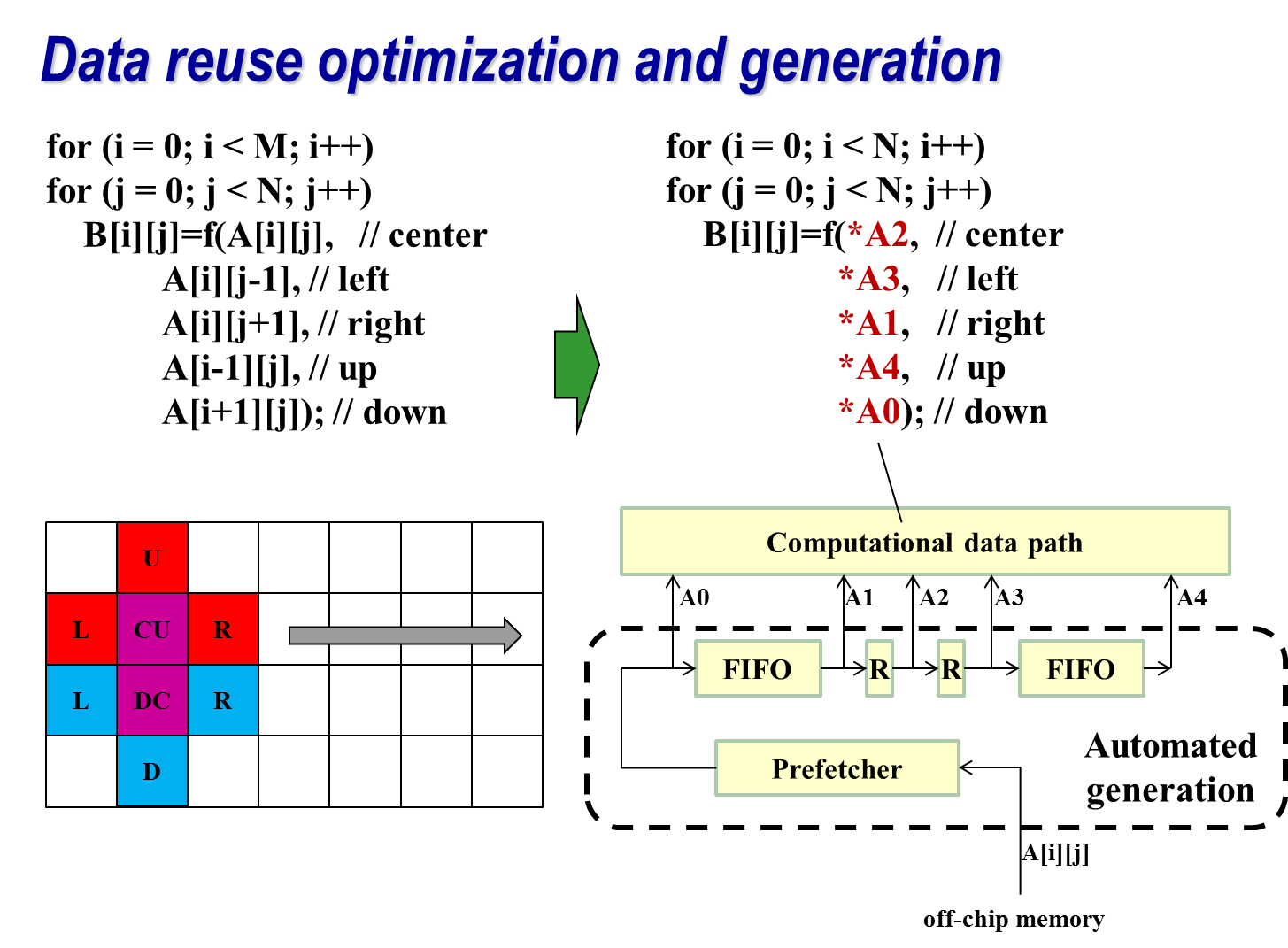

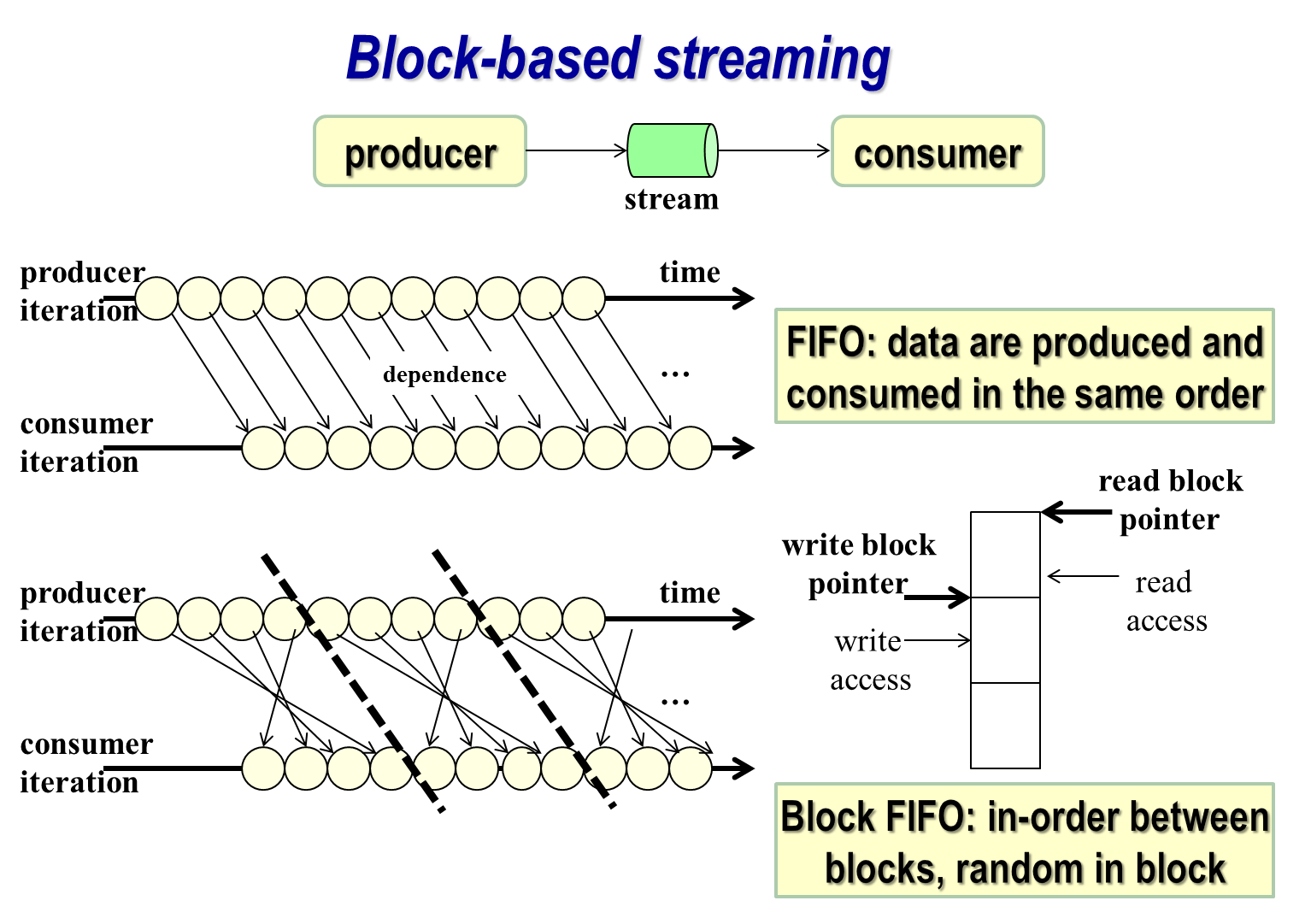

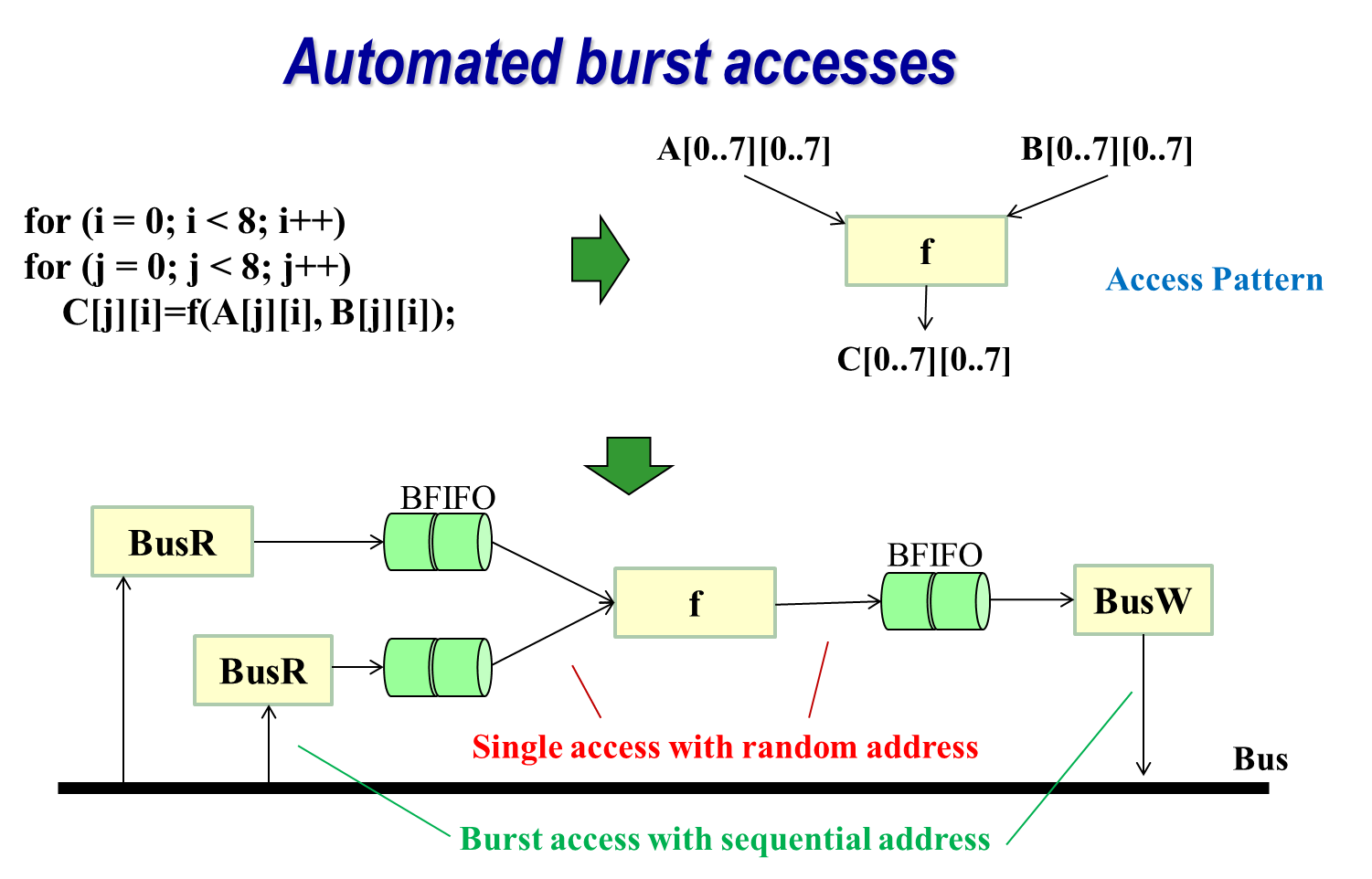

Various useful system design optimizations have been automated in the CMOST design flow. For the computation optimization, module selection and duplication determines for each module, what is the proper design option and how many hardware copies used to implement the module. For memory hierarchy optimization, data reuse schemes are explored automatically to find a good tradeoff between off-chip bandwidth saving and on-chip memory utilization. For communication optimization, the access pattern of producer tasks and consumer tasks are automatcially matched to create streaming buffers, and the corresponding address mapping are also performed to better utilize the switching buffer allocated. In addition, the accesses to buses and external memories are automatically packed into bursts to improve the access efficiency.

Software Release