EDACafe Broadcast: Interview with Phil Kaufman Award Winner Dr. Jason Cong, Professor, UCLA

https://edacafe.com/video/1/2001268/media.html

Meet UCLA's Dr. Jason Cong, 2024 Phil Kaufman Award Recipient

Podcast EP249: A Conversation with Dr. Jason Cong, the 2024 Phil Kaufman Award Winner

Dr. Jason Cong to be honored with 2024 Phil Kaufman Award

https://www.semiconductor-digest.com/dr-jason-cong-to-be-honored-with-2024-phil-kaufman-award/

How cutting-edge computer chips are speeding up the AI revolution

Engineers are harnessing the powers of graphics processing units (GPUs) and more, with a bevy of tricks to meet the computational demands of artificial intelligence.

Please read full article at the following link:

https://www.nature.com/articles/d41586-024-01544-0

Interview of Prof. Jason Cong by the IEEE Circuits and Systems Magazine

We are pleased to share the interview of Prof. Jason Cong by the IEEE Circuits and Systems Magazine, Prof. Yiran Chen, EiC, and Prof. Fan Chen, the Associate Editor.

https://ieeexplore.ieee.org/document/10378993

Prof. Cong's article published on the Semiconductor Engineering Magazine, IEEE Robert N. Noyce Medal

Toward Democratized IC Design And Customized Computing

How to make IC design more accessible to more people.

JUNE 28TH, 2022

BY: JASON CONG

https://semiengineering.com/toward-democratized-ic-design-and-customized-computing/

Live Q & A with the 2022 IEEE Robert N. Noyce Medal Honoree - Jingsheng Jason Cong

For fundamental contributions to electronic design automation and FPGA design methods.

Please see Youtube link:

https://www.youtube.com/watch?v=7rqTF8ibpiw

Alumnus Jason Cong's IEEE Robert N. Noyce Medal Represents an Impactful Computing Career Emboldened by the Right Choices | Computer Science | UIUC

When Illinois Computer Science alumnus Jason Jingsheng Cong (MS CS '87, PhD '90) left his home in China to become a graduate student here, he did so with one thought in mind. He wanted to study combinatorial mathematics and algorithms with longtime CS professor Dave Chung-Laung Liu.

Please read full article at the following link:

Congratulations to Prof. Jason Cong for receiving the 2022 IEEE Robert N. Noyce Medal

Congratulations to Prof. Jason Cong for receiving the 2022 IEEE Robert N. Noyce Medal “For fundamental contributions to electronic design automation and FPGA design methods.” The IEEE Robert N. Noyce Medal is a science award presented by the IEEE for outstanding contributions to the microelectronics industry. The medal is named in honour of Robert N. Noyce, the founder of Intel Corporation. He was also renowned for his 1959 invention of the integrated circuit. The medal is funded by Intel Corporation and was first awarded in 2000. The past winners include TSMC Founder and CEO Morris Chang, Intel CEO Craig Barrett, and most recently AMD CEO Lisa Su.

https://samueli.ucla.edu/ucla-engineering-professor-jason-cong-receives-2022-ieee-noyce-medal/

Remembering C.L. Dave Liu, Renowned Illinois CS Professor | Computer Science | UIUC

https://cs.illinois.edu/news/remembering-dave-liu-renowned-illinois-cs-p...

Xilinx Acquires Assets of Falcon Computing Solutions to Advance Software Programmability and Expand Developer Community

Please read the full story at the following link:

Benchmarking quantum layout synthesis

Computer scientists at the University of California Los Angeles found that current compilers for quantum computers are inhibiting optimal performance and argue that better quantum compilation design could help improve computation speeds up to 45 times.

The team designed a family of benchmark quantum circuits with known optimal depths or sizes, which could be used to improve quantum layout synthesis tools. They tested their benchmarks in four of the most used quantum compilation tools.

Please read the full story at the following link:

https://semiengineering.com/power-performance-bits-oct-20/

Prof. Cong appointed as the Volgenau Chair for Engineering Excellence in the Samueli School of Engineering

Professor Jason Cong has been appointed as the Volgenau Chair for Engineering Excellence in the Samueli School of Engineering. Prof. Cong joined the UCLA faculty in 1990. He is the Director of Center for Domain-Specific Computing (funded by an NSF Expeditions in Computing Award) and the Director of VLSI Architecture, Synthesis, and Technology (VAST) Laboratory. From 2005 to 2008, he served as the chair of the UCLA Computer Science Department. His research interests include electronic design automation, customized computing, quantum computing, and highly scalable algorithms. He is a Fellow of ACM and IEEE and a member of National Academy of Engineering.

Link to UCLA Computer Science Department News:

UCLA is selected as one of the four world-class universities by Xilinx to establish Adaptive Computer Research Clusters

Xilinx Teams with Leading Universities Around the World to Establish Adaptive Compute Research Clusters to spearhead novel research into all areas of adaptive compute acceleration.

The cluster at UCLA will focus on energy-efficient computing, customized computing for big-data applications and highly scalable algorithms. Prof. Jason Cong, Director for the Center for Customizable Domain-Specific Computing at UCLA Samueli School of Engineering, will lead the effort. Prof. Cong has been at the forefront of FPGA technology research for more than 30 years.

For more information, please visit https://www.xilinx.com/news/press/2020/xilinx-teams-with-leading-universities-around-the-world-to-establish-adaptive-compute-research-clusters.html

Professors from MIT, UCLA to be Honored for Excellence in Semiconductor Research

Please read the full story at the following link:

Jason Cong and Song-Chun Zhu: Center for Research in Intelligent Storage and Processing in Memory (CRISP)

We are pleased to announce that Professors Jason Cong (CS) and Song-Chun Zhu (CS and Statistics) are part of the University of Virginia’s new $27.5M Center on Research in Intelligent Storage and Processing in Memory (CRISP)—one of six Joint University Microelectronics Program (JUMP) centers nationwide that are managed by the Semiconductor Research Corporation with cost-sharing from DARPA. Each research center will examine a different challenge in advancing microelectronics—a field that is crucial to the U.S. economy and its national defense. The six JUMP centers are located at the University of Virginia, UC Santa Barbara, Carnegie Mellon, Purdue, University of Michigan and Notre Dame.

UV’s CRISP Center will bring together researchers from eight universities in an effort to remove the separation between memories that store data and processors that operate on that data—a separation that has been part of all mainstream computing architectures since 1945 when von Neumann first outlined how programmable computers should be structured. Unfortunately, that technology led to today's “memory wall” in which data access has become a major performance bottleneck. Professors Cong and Zhu will work with CRISP researchers and become instrumental in removing that bottleneck.

UCLA and Cornell Research Team Win Award from Intel and the National Science Foundation for Heterogeneous Computing Research Effort

Please read the full press at the following link:

Prof. Cong giving keynote at CNCC'2017

Prof. Cong delivered a keynote speech at the 2017 China National Computer Congress (CNCC) on October 27, 2017 held in Fuzhou, China. The title of Prof. Cong's speech is "Computing Near the End of Moore’s Law". Prof. Cong is awarded "Distinguished Contribution Award" by the China Computer Federation (CCF) on CNCC.

Slides available here: http://vast.cs.ucla.edu/~cong/slides/cncc2017_final_JasonCong.pdf

Related News: http://www.ccf.org.cn/c/2017-09-27/614976.shtml

http://www.ccf.org.cn/c/2017-10-30/617832.shtml

Prof. Cong's induction to the National Academy of Engineering

Prof. Jason Cong was inducted to the National Academy of Engineering on Oct. 8, 2017 in Washington DC for pioneering contributions to application-specific programmable logic via innovations in field-programmable gate array synthesis.

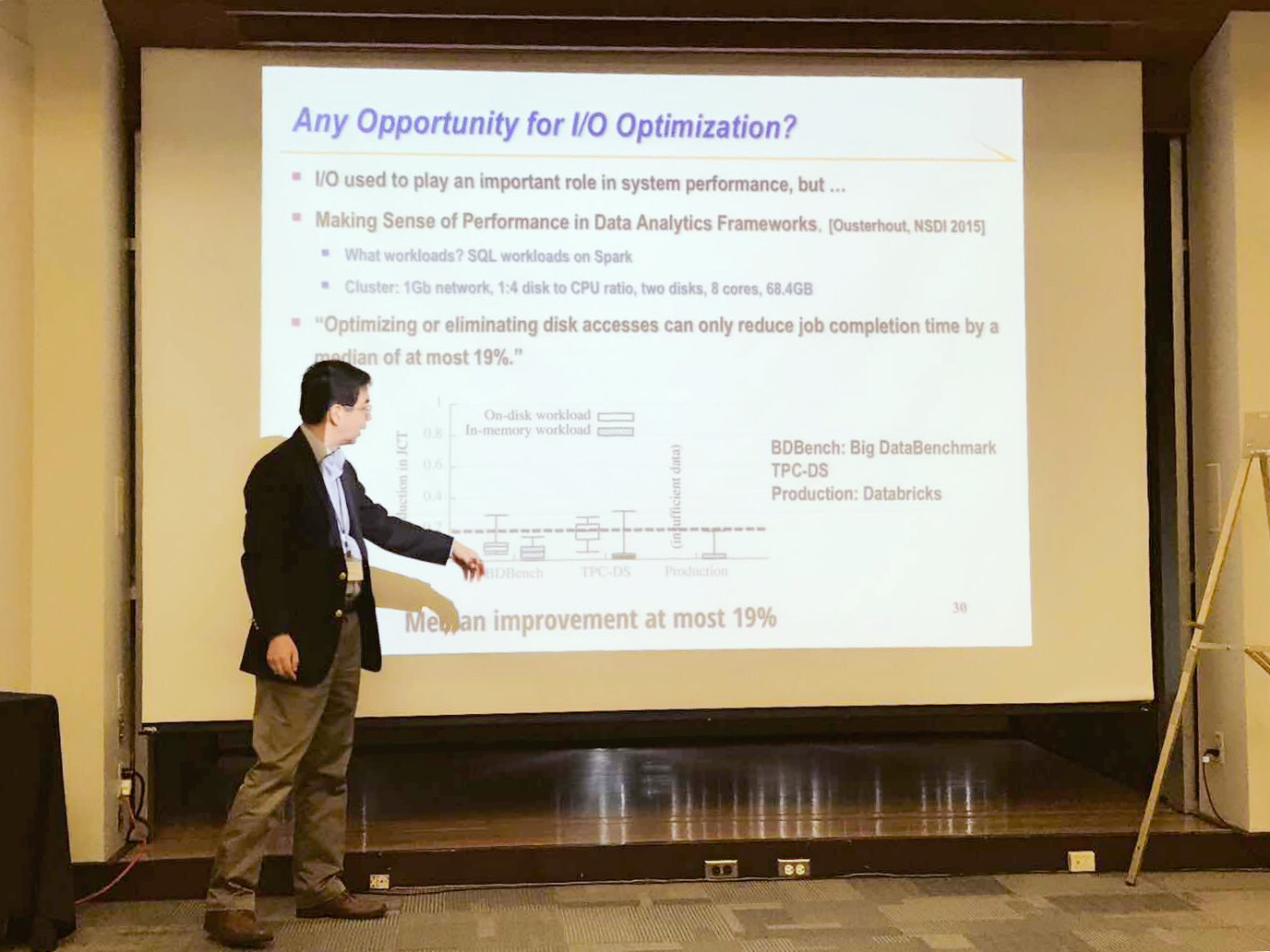

Prof. Cong giving keynote at IISWC'2017

Prof. Cong delivered a keynote speech at the 2017 IEEE International Symposium on Workload Characterization (IISWC'17) on October 2, 2017 held in Seattle, WA. The title of Prof. Cong's speech is "Characterization and Acceleration for Genomic Sequencing and Analysis". The talk covers background on genomic processing pipeline, workload characterization and optimization and acceleration developed in the group.

Slides available here:

http://vast.cs.ucla.edu/~cong/slides/IISWC_keynote_JasonCong.pdf

Best Paper Award at MEMSYS 2017: Authors Cong, Fang, Gill, Javadi, Reinman

Computer Science Department authors Jason Cong, Zhenman Fang, Michael Gill, Farnoosh Javadi, and Glenn Reinman have received a Best Paper Award at MEMSYS 2017 (2-5 October, Washington DC) for their recent paper AIM: Accelerating Computational Genomics through Scalable and Noninvasive Accelerator-Interposed Memory (https://memsys.io/). An abstract of this paper follows:

Computational genomics plays an important role in health care, but is computationally challenging as most genomic applications use large data sets and are both computation-intensive and memory-intensive. Recent approaches with on-chip hardware accelerators can boost computing capability and energy efficiency, but are limited by the memory requirements of accelerators when processing workloads like computational genomics. In this paper we propose the accelerator-interposed memory (AIM) as a means of scalable and noninvasive near-memory acceleration. To avoid the high memory access latency and bandwidth limitation of CPU-side acceleration, we design accelerators as a separate package, called AIM module, and physically place an AIM module between each DRAM DIMM module and conventional memory bus network. Experimental results for genomic applications confirm the benefits of AIM. Due to the much lower memory access latency and scalable memory bandwidth, our non-invasive AIM achieves much better performance scalability than the CPU-side acceleration when the memory system scales up.

Customizable Accelerated Computing Will Be Used in Brain Research

This collaborative work involves a team of researchers from several areas of UCLA. Professor Jason Cong and Professor Tad Blair from UCLA’s Brain Research Institute are refining the wireless miniscope to give it built-in, energy-efficient computing capability for real-time feedback and analysis.

Please read about this ground-breaking research on the UCLA Newsroom website:

http://newsroom.ucla.edu/releases/8-3-million-grant-from-national-science-foundation-will-help-ucla-spread-technology-behind-mini-microscope

CDSC Will Develop Customizable Computing Technology for Augmented Reality Funded by Intel and NSF

The full press release is available at:

http://engineering.ucla.edu/augmented-reality-making-it-secure-fast-efficient-and-resilient/

Prof. Jason Cong was the Featured Speaker of the Future Forum’s Lecture Series on “Understanding Future" on Aug. 11, 2017

Prof. Jason Cong was invited to give a talk "Computing at the End of Moore’s Law" at Future Forum'17 in China. Please see the slides here.

Here is video link of the talk (in Chinese)

Related News:

http://news.xinhuanet.com/2017-08/14/c_136525420.htm

http://news.e-works.net.cn/category6/news73429.htm

Amazon F1 FPGA in School & Research Fetures Prof. Cong's CS133 course ( Jie Wang, Pranav Thulasiram Bhat as TA)

FPGAs In School & Research

Research groups and graduate classes at top-tier universities contacted via AWS Educate and were eager to gain access to F1 instances.

UCLA‘s CS133 class (Parallel and Distributed Computing) is setting up an F1-based FPGA lab that will be operational within 3 or 4 weeks. According to UCLA Chancellor’s Professor Jason Cong, they are expanding multiple research projects to cover F1 including FPGA performance debugging, machine learning acceleration, Spark to FPGA compilation, and systolic array compilation.

Full Release is here:

https://aws.amazon.com/blogs/aws/ec2-f1-instances-with-fpgas-now-generally-available/

Peng Wei for 2016-2017 Symantec Outstanding Graduate Student Research Award

Congratulations to Peng Wei (advisor: Prof. Jason Cong) for receiving the 2016-2017 Symantec Outstanding Graduate Student Research Award.

Bingjun Xiao for 2016 EDAA Outstanding PhD Dissertation Award

Congratulations to Bingjun Xiao (PhD’2015, advisor, Jason Cong), whose dissertation "Communication Optimization for Customizable Domain-Specific Computing", has been awarded the 2016 EDAA Outstanding PhD Dissertation Award. The award was presented at the conference DATE 2017 – Design, Automation & Test in Europe, on Mar 28 in Lausanne, Switzerland.

The full press release of EDAA is available at http://www.edaa.com/press_releases/EDAA_Award_2016_Results.pdf

EDAA is a non-profit association. Its purpose is to operate for educational, scientific and technical purposes for the benefit of the international electronics design and design automation community. The Association, in the field of design and design automation of electronic circuits and systems, promotes a series of high quality technical international conferences and workshops across Europe and cooperates actively to maintain harmonious relationships with other national and international technical societies and groups promoting the purpose of the Association. EDAA is the main sponsor of DATE, the premier Design, Automation and Test Conference and Exhibition in Europe.

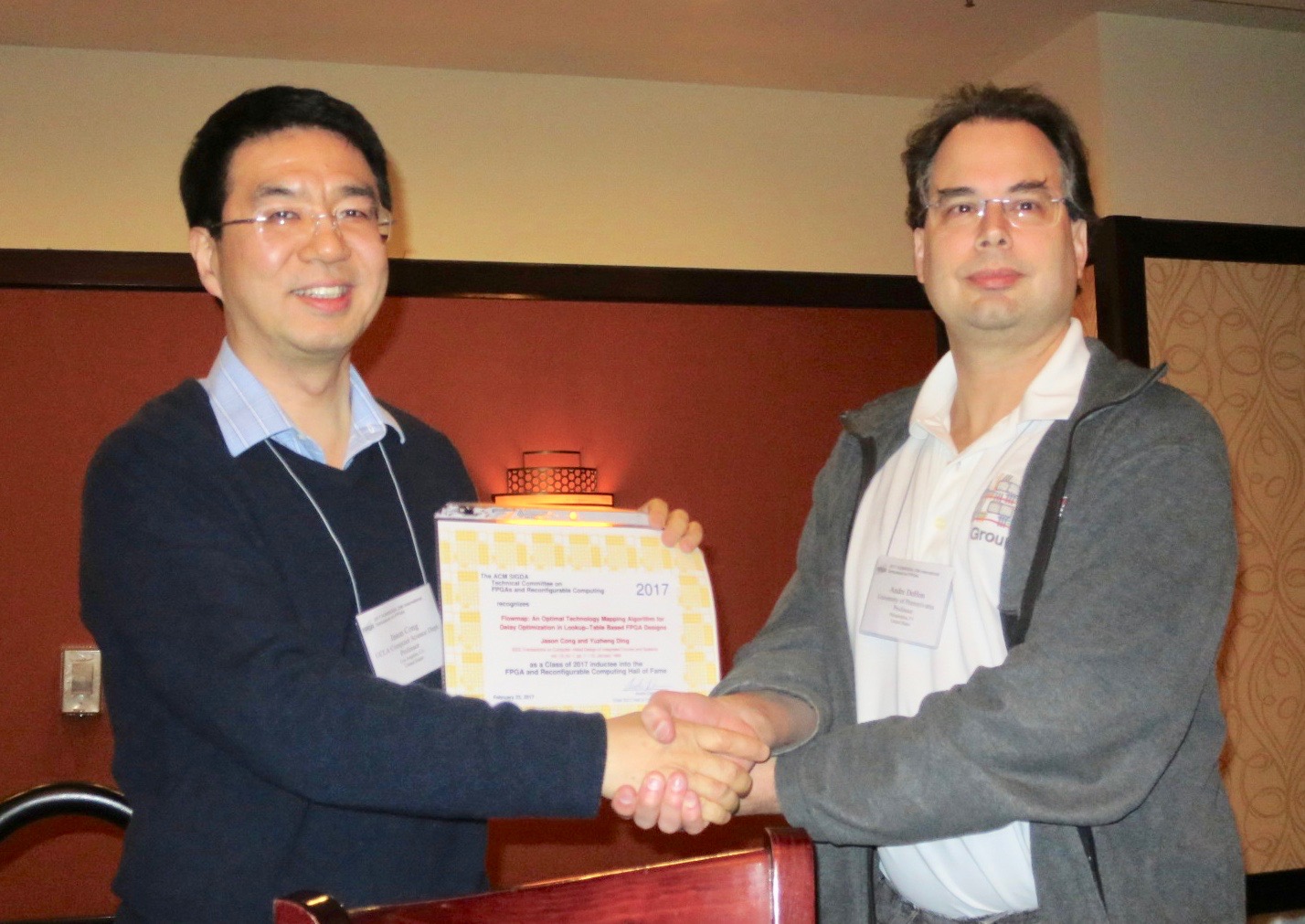

ACM/SIGDA TCFPGA initiated the FPGA and Reconfigurable Computing Hall of Fame program at the symposium

In celebrating the 25th anniversary of the FPGA Symposium, which took place February 22nd through 24th in Monterey, California, ACM/SIGDA TCFPGA initiated the FPGA and Reconfigurable Computing Hall of Fame program at the symposium. The paper entitled “FlowMap: An Optimal Technology Mapping Algorithm for Delay Optimization in Lookup-Table Based FPGA Designs” by Prof. Jason Cong and his former PhD student Dr. Eugene Ding published in IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 1994, was inducted to the inaugural class of the Hall of Fame (http://hof.tcfpga.org). The endorsement letter is available at http://hof.tcfpga.org/wp-content/uploads/2017/02/flowmap1994_class2017.pdf.

About ACM FPGA: The ACM/SIGDA International Symposium on Field-Programmable Gate Arrays, held annually in Monterey, is the premiere forum for the presentation of advances in all areas of FPGA technology. http://www.isfpga.org/.

UCLA Pioneers elected to National Academy of Engineering

Three faculty members of the UCLA Henry Samueli School of Engineering and Applied Science – Jason Cong and George Varghese of Computer Science, and Behzad Razavi of Electrical Engineering (pictured left to right above) – have been elected to the National Academy of Engineering, among the highest honors that can be accorded to an American engineer. The academy announced the 2017 class of 84 members and 22 foreign members on February 8.

With the election of Cong, Varghese and Razavi, UCLA Engineering has 35 affiliated faculty members who are members of the National Academy of Engineering.

Jingsheng Jason Cong, Distinguished Chancellor’s Professor of Computer Science, was recognized by the academy “for pioneering contributions to application-specific programmable logic via innovations in field programmable gate array (FPGA) synthesis.”

George Varghese, Chancellor’s Professor of Computer Science, was recognized by the academy “for network algorithmics that make the Internet faster, more secure, and more reliable.”

Behzad Razavi, Chancellor’s Professor of Electrical Engineering, was recognized by the academy “for contributions to low-power broadband communication circuits.”

For more details, please visit http://engineering.ucla.edu/ucla-pioneers-in-customized-computing-communication-circuits-networking-elected-to-national-academy-of-engineering/

For Peking University press release, please visit: http://news.pku.edu.cn/xwzh/2017-02/19/content_296744.htm

For World Journal press, please visit http://www.worldjournal.com/4846224/article-叢京生獲選國家工程學院院士/

Prof. Cong Received ASP-DAC'17 10-Year Retrospective Most Influential Paper Award

Prof. Jason Cong and his former students Guojie Luo, Jie Wei, and Yan Zhang received received the 10-Year Retrospective Most Influential Paper Award at 2017 Asia and South-Pafacific Design Automation ASP-DAC'17 in Tokyo, Japan on Jan. 17, 2017 for their paper entitled "Thermal-Aware 3D IC Placement Via Transformation” published in ASP-DAC in 2007. Prof. Cong’s group also received another 10-Year Retrospective Most Influential Paper Award at ASP-DAC’2015 two years ago.

ASP-DAC 2017 is the twenty-second annual international conference on VLSI design automation in Asia and South Pacific region, one of the most active regions of design and fabrication of silicon chips in the world. The conference aims at providing the Asian and South Pacific CAD/DA and Design community with opportunities of presenting recent advances and with forums for future directions in technologies related to Electronic Design Automation (EDA). ASP-DAC cultivates and promotes interactions and presentations of novel ideas among EDA researchers/developers and system/circuit/device-level designers. It is attended by scientists, engineers, researchers, and students who are interested in theoretical and practical aspects of VLSI design and design automation worldwide.

ASP-DAC'17 website: www.aspdac.com/aspdac2017/

From IEEE Computer Society Announcement on Feb. 22, 2016

Dr. Jason Cong, a Chancellor’s Professor at the Computer Science Department, with joint appointment from Electrical Engineering Department of University of California, Los Angeles, has been selected to receive the 2016 Technical Achievement Award “For setting the algorithmic foundations for high-level synthesis of field programmable gate arrays”.

The IEEE Computer Society Technical Achievement Award is given for outstanding and innovative contributions to the fields of computer and information science and engineering or computer technology, usually within the past 10, and not more than 15, years. Contributions must have significantly promoted technical progress in the field. The complete IEEE Computer Society announcement is available at https://www.computer.org/web/pressroom/cong-tech-achievement

Dr. Cong, elected to an IEEE Fellow in 2000 and ACM Fellow in 2008, is the recipient of the 2010 IEEE Circuits and System (CAS) Society Technical Achievement Award “For seminal contributions to electronic design automation, especially in FPGA synthesis, VLSI interconnect optimization, and physical design automation.” Dr. Cong is the only award recipient to receive the Technical Achievement Award from both the IEEE Computer Society and the IEEE CAS.

The youtube video is here: https://www.youtube.com/watch?v=tAUWwjIJ_Ss

TECH DESIGN FORUM: Minimize memory moves for greener data centers

The news about Prof. Jason Cong's speaking at the DAC 2016.

http://www.techdesignforums.com/blog/2016/06/08/dac-data-center-acclerat...

NEXTPLATFORM: Broader Paths Etched into FPGA Datacenter Roadmap

There is news release about Prof. Cong's Research. http://www.nextplatform.com/2016/02/29/broader-paths-etched-into-fpga-datacenter-roadmap/

US CHINA PRESS: Prof. Cong gave talk at Grand Opening Semiar for UCLA Chinese-American Students and Scholars Seminar(UCLA-C3S) (Apr. 2015)

Prof. Cong gave talk entitled as "Can We Design Our Career" at Grand Opening Seminar for UCLA Chinese-American Students and Scholars Seminar (UCLA-C3S).

http://news.uschinapress.com/2015/0414/1019369.shtml

UCLA Newsroom : Prof Cong Received ASPDAC Ten-Year Retrospestive Most Influential Paper Award (Jan. 2015)

A research paper by Jason Cong, a Chancellor’s Professor in UCLA’s Computer Science Department, and his former doctoral student, Yan Zhang, was selected as the 10-Year Retrospective Most Influential Paper in the 2015 Asia South-Pacific Design Automation Conference (ASPDAC). The award for the paper, “Thermal-Driven Multilevel Routing for 3-DICs,” was presented at the opening ceremony of ASPDAC’15 on Jan. 20, in Chiba/Tokyo, Japan.

Cong, on faculty at the UCLA Henry Samueli School of Engineering and Applied Science, is the director of Center for Domain-Specific Computing, co-director of UCLA/Peking University Joint Research Institute in Science and Engineering and co-director of the VLSI CAD Laboratory. His research interests include synthesis of VLSI circuits and systems, programmable systems, novel computer architectures, nano-systems and highly scalable algorithms. He has over 350 publications in these areas and has won seven best paper awards and the 2011 ACM/IEEE A. Richard Newton Technical Impact Award in Electric Design Automation.

He was elected to an IEEE Fellow in 2000 and ACM Fellow in 2008. He is the recipient of the 2010 IEEE Circuits and System Society Technical Achievement Award "for seminal contributions to electronic design automation, especially in FPGA synthesis, VLSI interconnect optimization, and physical design automation."

NSF Press: Awarded $3 million InTrans grant by NSF & Intel (July. 2014)

In partnership with Intel Corporation, NSF announced the first InTrans award of $3 million to a team of researchers led by Professor Jason Cong who are designing customizable, domain-specific computing technologies for use in healthcare. The work could lead to less exposure to dangerous radiation during x-rays by speeding up the computing side of medicine. It also could result in patient-specific cancer treatments. Led by University of California, Los Angeles, the research team includes experts in computer science and engineering, electrical engineering and medicine from Rice University and Oregon Health and Science University. The team comes mainly from the Center of Domain-Specific Computing (CDSC), which was supported by an NSF Expeditions in Computing Award in 2009.

In the project, the researchers looked beyond parallelization (the process of working on a problem with more than one processor at the same time) and instead focused on domain-specific customization, a disruptive technology with the potential to bring orders-of-magnitude improvements to important applications. Domain-specific computing systems work efficiently on specific problems - in this case, medical imaging and DNA sequencing of tumors - or a set of problems with similar features, reducing the time to solution and bringing down costs.The InTrans program not only advances important fundamental research and integrates it into industry, it also benefits society by improving medical imaging technologies and cancer treatments, helping to extend lives.

For details, please see NSF and UCLA press releases:

Taking great ideas from the lab to the fab

First NSF InTrans Grant Awarded to UCLA

UCLA Today : Jason Cong awarded for outstanding electronic design automation (June 2011)

Jason Cong, Chancellor’s Professor of Computer Science at the UCLA Henry Samueli School of Engineering and Applied Science, received this year’s A. Richard Newton Technical Impact Award in Electronic Design Automation from the Association of Computer Machinery/Institute of Electrical and Electronics Engineers (ACM/IEEE). He shares the award with his former Ph.D. student, Eugene Ding, now with Xilinx. Cong and Ding received the award for “pioneering work on technology mapping for FPGA (field-programmable gate array) that has made a significant impact on the FPGA research community and industry,” as evidenced by their paper “FlowMap: An Optimal Technology Mapping Algorithm for Delay Optimization in Lookup-Table Based FPGA Designs” (IEEE Transactions on Computer-Aided Design, vol 13, no. 1, pp. 1-12, January 1994).

http://today.ucla.edu/portal/ut/jason-cong-receives-acm-ieee-a--richard-newton-technical-impact-award-in-electronic-design-automation.aspx (photo)

UCLA Newsroom : Engineering entrepreneurs: Taking university research to the public (February 2011)

AutoESL was founded directly by faculty and graduate students from the UCLA Henry Samueli School of Engineering and Applied Science. Using the technology licensed from UCLA, AutoESL found a critical niche in developing tools that reduce design time and improve the quality of integrated circuit design, and in less than five years, the company became an acquisition target for Xilinx. "I believe that university spinoffs involving the developers of the original technology are the best way to bridge such gaps." - said by Jason Cong, Chancellor's Professor in computer science at UCLA Engineering and a co-founder of AutoESL, worked with UCLA Engineering graduate students in developing the technology.

http://newsroom.ucla.edu/portal/ucla/engineering-entrepreneurs-taking-192876.aspx

Society News : IEEE CAS Awards 2010 (July 2010)

Prof. Jason Cong is the recipient of the 2010 IEEE Circuits and System (CAS) Society Technical Achievement Award. This award honors the individual whose exceptional technical contributions to a field within the scope of the CAS Society have been consistently evident over a period of years. The citation of the award for Prof. Cong reads “For seminal contributions to electronic design automation, especially in FPGA synthesis, VLSI interconnect optimization, and physical design automation”. Prof. Cong will receive the award at the IEEE International SoC Conference on September 27. 2010.

http://cassnewsletter.org/Volume4-Issue3/Society_News.html (photo)

US News : Customized Computing for Health Care (July 2010)

Researchers at UCLA are designing new targeted types of computer software and hardware --a field known as domain-specific computing--to develop a health care computing prototype that could enable physicians to use computers in speedier, cost-efficient and much more focused ways. The work is supported by a $10 million grant over five years from the National Science Foundation as part of the American Recovery and Reinvestment Act of 2009. Cong and others believe that domain-specific computing, which uses “customizable” hardware and computer languages tailored to a particular application, will use less energy and produce faster results.

http://www.usnews.com/science/articles/2010/07/26/customized-computing-for-health-care.html

Science China : The Opening of? the Third U.S. – China Computer Science Leadership Summit (June 2010)

The Third U.S. – China Computer Science Leadership Summit was held in Peking University, China. Prof. Cong was invited to give a talk in the summit as professor from UCLA and Chang Jiang Scholar of Peking University.

http://www.scichina.com:8083/sciF/CN/column/item527.shtml

FPGA JOURNAL : A Perfect DSP Storm -- BDTi + High Level Synthesis +FPGA (January 2010)

AutoESL was spun out of the prolific UCLA program of Prof. Jason Cong - long time FPGA advocate and expert. AutoESL's AutoPilot takes C, C++, and SystemC as inputs. AutoPilot uses the popular and capable LLVM (low-level virtual machine) compiler, so adding new high-level languages should be a comparatively simple matter. The high-level synthesis "guts" are de-coupled from the language front-end somewhat, so the scheduling and allocation magic can be more or less language independent. In this phase of high-level synthesis adoption where input language is still a question mark, that's a good strategy.

http://www.fpgajournal.com/fpgajournal/feature_articles/20100119-storm/

People’s Daily : China’s 60th Anniversary Celebration (October 2009)

Prof. Cong was invited by the Chinese government as a member of the delegation of distinguished oversea scientists and scholars to participate in the National Day celebration for China's 60th? Anniversary.

http://www.chinanews.com.cn/lxsh/news/2009/10-09/1901554.shtml

UCLA Newsroom : NSF awards UCLA $10 million to create customized computing technology (August 2009)

The UCLA Henry Samueli School of Engineering and Applied Science has been awarded a $10 million grant by the National Science Foundation's Expeditions in Computing program to develop high-performance, energy efficient, customizable computing that could revolutionize the way computers are used in health care and other important applications. Professor Jason Cong will be the Director of the new UCLA Center for Domain-Specific Computing (CDSC), which will oversee the research.Research being conducted by the CDSC is a collaborative effort among faculty from UCLA's engineering school, medical school and applied mathematics program, as well as faculty from Rice University, Ohio State University and UC Santa Barbara. In particular, Professors Jens Palsberg, Miodrag Potkonjak and Glenn Reinman from the UCLA CS Dept will also be involved in the Center. Congratulations to Professor Cong and all the faculty involved in the center.

http://newsroom.ucla.edu/portal/ucla/ucla-engineering-awarded-10-million-97818.aspx

PKU News : Agreement Signing for the PKU-UCLA Joint Research Institute for Science and Engineering (June 2009)

Prof. Cong attended the agreement signing ceremony for the PKU-UCLA joint research program for science and engineering and was appointed as the founding co-director of the PKU/UCLA Joint Research Institute.

http://pkunews.pku.edu.cn/xwzh/2009-06/21/content_151050.htm

EE Times : Future of chip design revealed at ISPD (May 2008)

Another paper of note, according to ISPD general chair David Pan, an EE Professor at the University of Texas (Austin), was one showing how to create ultra-high-speed on-chip interconnects using radio frequency (RF) transmission lines. This was presented by Professors Frank Chang and Jason Cong of the University of California at Los Angeles (UCLA). In this interconnect scheme, data is transmitted by modulating an electromagnetic wave along an RF transmission line that can be implemented using standard CMOS processing steps.

http://www.eetimes.com/news/design/showArticle.jhtml?articleID=207400313

SCDsource : Multi-band RF interconnect speeds network-on-chip (January 2008)

Researchers at the University of California at Los Angeles (UCLA) have developed a multi-band RF interconnect technology that boosts communications speeds and reduces latency in multicore ICs. The technology will "open a new wave in on-chip communications," says Jason Cong, chairman of UCLA's computer science department.

http://www.scdsource.com/academic.php?id=77

'Huge Opportunity' in IC Design Optimization Gained by Semiconductor Research Corporation, National Science Foundation (December 2007)

RESEARCH TRIANGLE PARK, N.C. - Research at UCLA sponsored by Semiconductor Research Corporation (SRC), the world's leading university research consortium for semiconductors and related technologies, and the National Science Foundation (NSF) celebrated today CAD techniques that will facilitate advances for multiple technology generations. The resulting optimization methods can provide improvements equivalent to the investment of billions of dollars in fabrication equipment costs.

"This is a huge opportunity for the industry as optimal placement of circuits in the design process will deliver scaling of semiconductors that is independent of feature size, providing Moore's Law progress at less cost than other options," said Professor Jason Cong, chair of the UCLA Computer Sciences Department (www.ucla.edu). "Closing such a large optimality gap will be equivalent to several technology generation advancements. In comparison, the introduction of copper interconnects was equivalent to a 30% interconnect length reduction, and so is each generation of device scaling, but each requires a multi-billion dollar investment."

https://www.src.org/newsroom/press-release/2007/41/

UCLA Newsroom : UCLA scientists working to create smaller, faster integrated circuits (December 2007)

Integrated circuits are the "brain" in computers, cell phones, DVD players, iPhones, personal digital assistants, automobiles' navigation systems and anti-lock brakes, and many other electronic devices. A team of UCLA scientists has now demonstrated substantial improvements in integrated circuits, achieved not by costly improvements in manufacturing but by improved computer-aided design software based on better mathematical algorithms.

http://www.newsroom.ucla.edu/portal/ucla/ucla-scientists-make-major-advance-41151.aspx

SolidState Technology : Moore's Law to head z-ward? (November 2007)

While the industry struggles to continue on the Moore's Law track, 3D approaches superior to those of systems-on-chip may provide an interim solution if the shrink slows down. A SEMATECH-organized workshop in Albany, NY earlier this month (Oct. 11-12) addressed fundamental issues about 3D, including four reasons why every chipmaker has 3D/TSV approaches on its roadmap, and what needs to be solved before 3D can be effective beyond simple memory.

http://sst.pennnet.com/display_article/310451/5/ARTCL/none/none/1/Moore's-Law-to-head-z-ward?/

EE TIMES : Plain-vanilla EDA gets its due (September 2006)

These days, the excitement in EDA centers on electronic system-level tools and design-for-manufacturability. But usnsolved problems remain in plain-vanilla synthesis, placement and routing.

http://www.eetimes.com/showArticle.jhtml?articleID=188500070

EE TIMES : Optimization techniques rein in IC POWER FLOW (May 2006)

In the effort to save power consumption, chip designers increasingly are turning to such techniques as power gating--which requires behavioral simulation and intelligent placement of power-gating transistors--as well as voltage reduction, frequency scaling and limiting accesses to off-chip memory.

http://www.eetimes.com/news/design/showArticle.jhtml?articleID=187201880

FPGA JOURNAL : Blaming the Button -- Physical Synthesis Moves to Mainstream (April 2006)

According to a recent paper published by Jason Cong and Kirill Minkovich of UCLA, the optimality of logic design alone can be off by as much as 70-500X. That's not a percent sign, boys and girls; that big X means that your design may be taking up 70 to 500 times as many LUTs as the best possible solution. The UCLA study compared synthesis results from academic and commercial synthesis tools with known-optimal solutions for a variety of circuits. The paper says that the synthesis tools were 70 times larger in area on average than the known optimal solutions in the test study.

http://www.fpgajournal.com/articles_2006/20060425_button.htm

EE TIMES : Huge FPGA synthesis gap seen -- Circuits may be 70x larger than optimal (February 2006)

Anyone who thinks FPGA synthesis is a solved problem will get a rude awakening at the FPGA 2006 conference here this week. That's when an eminent CAD researcher will show that current synthesis tools may produce circuits that are 70 to 500 times larger than the known optimal solutions in synthetic benchmarks.

http://www.eetimes.com/news/latest/showArticle.jhtml?articleID=180204087

World Journal Daily About Prof. Cong's Talk in PUAASC 2005 Annual Convention : Design Our Career, or Can We? -- Reflection from an Engineering Professor

http://www.worldjournal.com/wj-la-news.php?nt_seq_id=1237232

FPGA JOURNAL : Power -- Suddenly, We Care (April 2005)

For years it was like a slogan. "FPGAs are nice, but they're power hogs." If a new FPGA family offered a 50% performance increase or doubled the LUT count over the previous generation, damn the heatsinks and full-speed ahead. Designers rolled FPGAs in with reckless abandon. Today, however, forces are conspiring to bring power concerns off of the back burner and into the forefront of FPGA design consideration.

http://www.fpgajournal.com/articles_2005/20050426_power.htm

EE TIMES : IC floor planning moves ahead (January 2005)

A new approach to IC floorplanning developed by UCLA researchers is said to reduce wire length while running orders of magnitude faster than previous solutions. The approach was disclosed at the recent ASP-DAC conference in Shanghai.

http://www.eetimes.com/showArticle.jhtml?articleID=59100114

FPGA JOURNAL : Training Tomorrow's Talent (August 2004)

Professor Jason Cong is profiled in the latest issue of FPGA and Programmable Logic Journal. Cong, who is described as a "modern-day luminary" and "master educator," has trained some of the best technical talent in the FPGA design tools industry today.

https://www.eejournal.com/article/20040831_cong/

EE TIMES : Power, crosstalk crisis to reroute IC design flows (April 2004)

Power and signal-integrity problems are approaching critical mass and will soon force changes in the nanometer IC design flow. But CAD methodology experts speaking at the Electronic Design Processes 2004 workshop said that the industry is on the case.

http://www.eetimes.com/article/showArticle.jhtml?articleId=19400044&sub_taxonomyID=4217

EE TIMES : FPGA placement performs poorly, study says (November 2003)

Timing-driven placement algorithms for FPGAs can be as much as 50 percent away from optimal results, according to a paper given at the 2003 International Conference on Computer-Aided Design (ICCAD).

http://www.eedesign.com/story/OEG20031113S0048

EE TIMES : Magma acquisition targets structured ASIC market (June 2003)

Making a bold entry into a marketplace barely touched by the big EDA vendors, Magma Design Automation confirmed that it has purchased Los Angeles-based PLD synthesis company Aplus Design Technologies to enter the emerging structured ASIC market.

http://www.eedesign.com/showArticle.jhtml?articleID=17408431

EE TIMES : IC placement benchmarks needed, researchers say (April 2003)

Following up on a controversial study that claimed IC placement algorithms are severely deficient, researchers at the International Symposium on Physical Design (ISPD) struggled to find a benchmarking methodology for IC physical design.

http://www.eedesign.com/showArticle.jhtml?articleID=17408299

EE TIMES : ISPD to present call for EDA benchmarking (April 2003)

A call for open benchmarking of IC placement tools will be among the topics at the 2003 International Symposium on Physical Design (ISPD). ISPD will also review the latest research in topics such as physical synthesis, timing, partitioning, power grid design, lithography, routing, and circuit fabrics.

http://www.eedesign.com/showArticle.jhtml?articleID=17408310

EE TIMES : Placement tools criticized for hampering IC designs (February 2003)

Current IC placement algorithms leave so much excess wire that chip designs are essentially several technology generations behind where they could be, according to a recent paper by researchers at the University of California at Los Angeles (UCLA).

http://www.eedesign.com/showArticle.jhtml?articleID=17408185

EE TIMES : FPGA synthesis tools lose battle with John Henry (February 2000)

In American folklore, John Henry represents man's struggle against obsolescence. Legend has it that John Henry and his sledgehammer beat a steam-powered drill in a tunnel-digging contest, but his heart burst in the effort. An evening panel at FPGA 2000 entitled "The John Henry Syndrome" recast that legend in the FPGA world, asking whether software tools can ever outpace human intervention.

http://www.eetimes.com/article/showArticle.jhtml?articleId=18303632

EE TIMES : Startup rethinks FPGA synthesis (February 2000)

An EDA startup with close ties to the University of California at Los Angeles (UCLA) is quietly preparing next-generation synthesis for large, high-performance PLDs. The startup, Aplus Design Technologies (ADT), came to light at the FPGA 2000 Conference in Monterey with the announcement of a partnership with Cypress Semiconductor Inc.

http://www.eedesign.com/showArticle.jhtml?articleID=17405549

EE TIMES : Panel debates synthesis-layout integration (April 1999)

The difficult issue of whether, and how, to integrate logical and physical design surfaced anew at the International Symposium on Physical Design (ISPD-99), where EDA vendors and academic professors joined a sometimes contentious panel on "layout-driven synthesis or synthesis-driven layout."

http://www.eetimes.com/article/showArticle.jhtml?articleId=18301566&sub_taxonomyID=4217

EE TIMES : ICCAD probes tools for billion-transistor designs (November 1998)

Architectural and physical design must be brought closer together to handle billion-transistor designs, according to panelists at this week's International Conference on Computer-Aided Design (ICCAD 98). The Semiconductor Industry Association's National Technology Roadmap predicts billion-transistor chips by 2010.

http://www.eetimes.com/article/showArticle.jhtml?articleId=18300460