Software description:

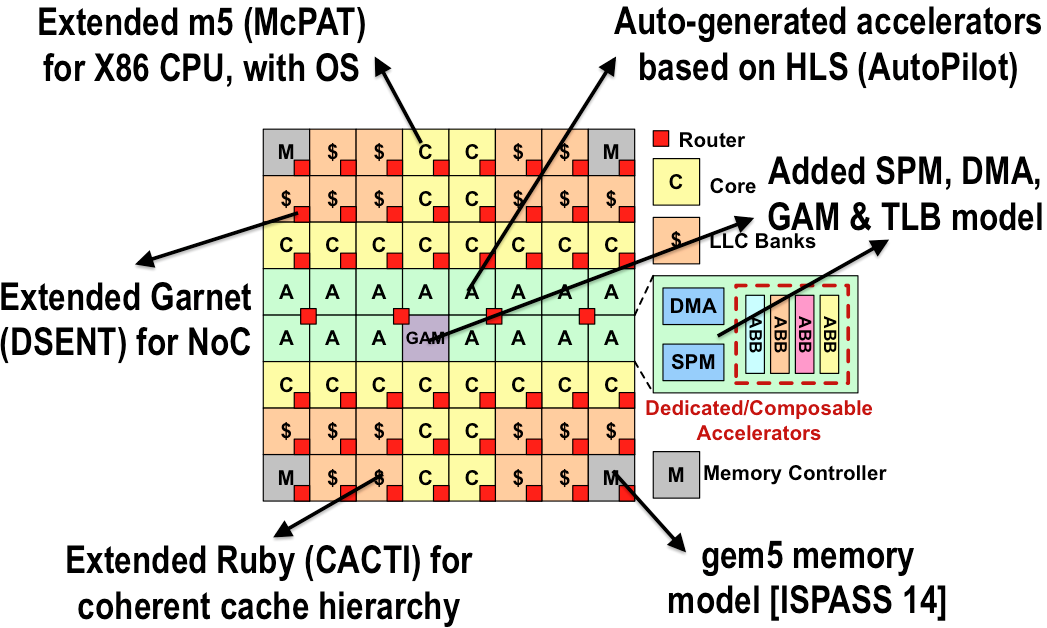

PARADE is a cycle-accurate full-system simulation platform that enables the design and exploration of the emerging accelerator-rich architectures (ARA). It extends the widely used gem5 simulator with high-level synthesis (HLS) support.

PARADE simulates ARA at system-level and provides following features:

- Full-system X86 support based on gem5

- Global Accelerator Management (GAM)

- Coherent cache/scratchpad with shared memory based on Ruby

- Customizable Network-on-Chip simulation based on Garnet

- Power/area simulation

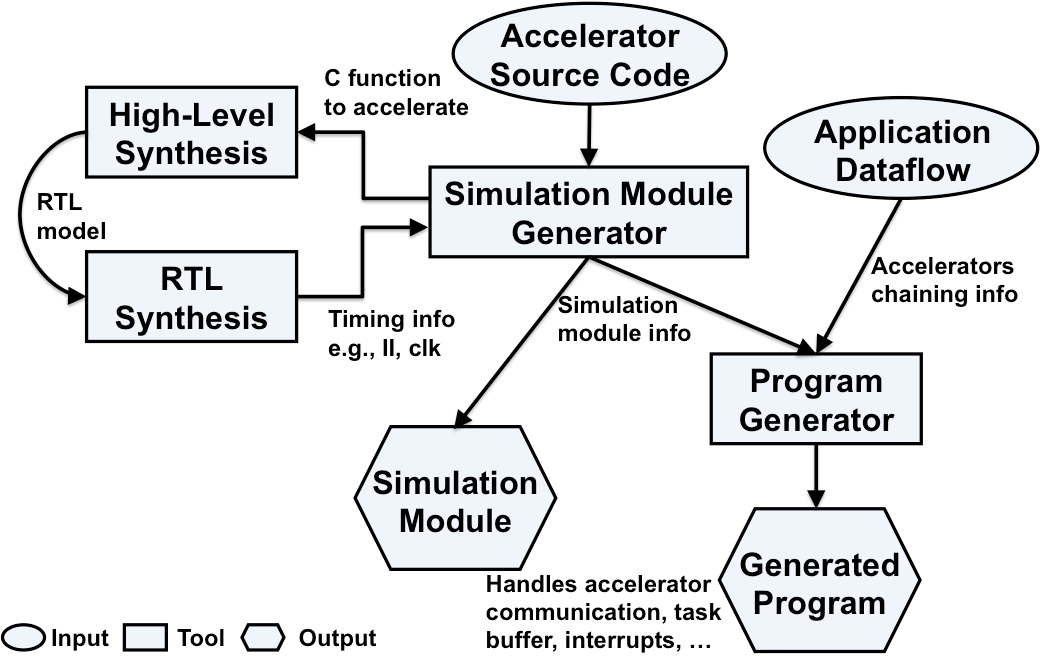

- Automatic accelerator/application generation based on HLS

Team Members:

Postdoc and students: Zhenman Fang, Michael Gill, Yuchen Hao

Faculty: Jason Cong, Glenn Reinman

Download:

PARADE is open source and available for download at github: https://github.com/cdsc-github/parade-ara-simulator

Here is the download link for disk image and Linux binaries that PARADE simulates.

Further Interest:

For more details, please read our ICCAD 15 paper and ISCA 15 tutorial, or contact Dr. Zhenman Fang.

If you use PARADE in your research, please cite our ICCAD 15 paper. Here is the bibtex to download.

Year:

2017