3-D ICs have recently attracted great interest from researchers and IC designers. Studies demonstrate a potential performance improvement of up to 65% by transferring a placement from 2-D to 3-D and eliminating long interconnects. Furthermore, the multiple device layer structure of 3-D ICs provides a platform to integrate different components, such as digital ICs, analog ICs, memory, RF modules, and different technologies such as SOI, SiGe HBTs, GaAs, etc., into one single circuit stack. Thus, it is a more flexible vehicle for system-on-chip (SoC) and system-in-package (SiP) designs compared to planar 2-D IC technologies.

Although 3-D integration shows promise, significant challenges associated with efficient circuit design and operation have hampered its adoption and further development. The most important issue in 3-D IC is heat dissipation. The thermal problem has already had an impact on the reliability and performance of high-performance 2-D ICs. The problem is aggravated in 3-D ICs, principally for two reasons: the devices are more packed, which results in higher power density; and the insulating dielectric layers between the device layers have much lower thermal conductivities than silicon. Furthermore, the third dimension brings both flexibility and difficulties to physical design algorithms. The existing 2-D metrics cannot be simply extended to generate similar metrics for 3-D designs. Take wirelength as an example: a ``bounding-cube'' might not have enough accuracy for wirelength estimation because of the existence of huge obstacles in z-direction. Also, a 3-D IC physical design problem is usually of higher complexity, with a much enlarged solution space due to the multiple device layer structure. Efficient 3-D physical designs tools, including 3-D floorplanning, placement and routing tools, that are specifically designed to take the thermal problem into consideration, are essential to 3-D IC circuit design.

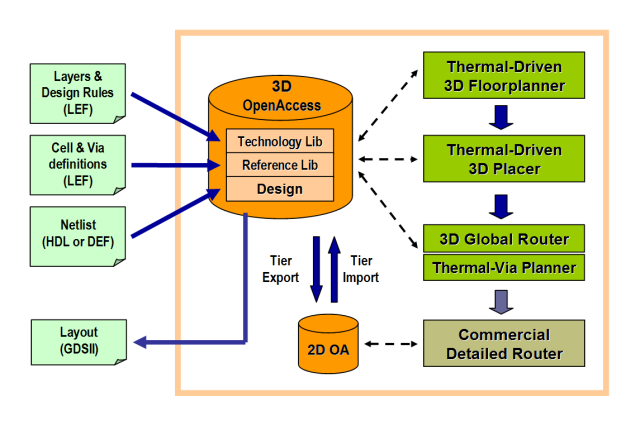

The following figure shows the 3-D physical design tool package that we are working on. Among the three major modules, we have completed the initial version of the floorplanning and routing tools and are working on the placement tool. Our group has also developed MEVA-3D, an automated physical design and architecture performance estimation flow for 3D architectural evaluation which includes 3D floorplanning, routing, interconnect pipelining and automated thermal via insertion, and associated die size, performance, and thermal modeling capabilities.

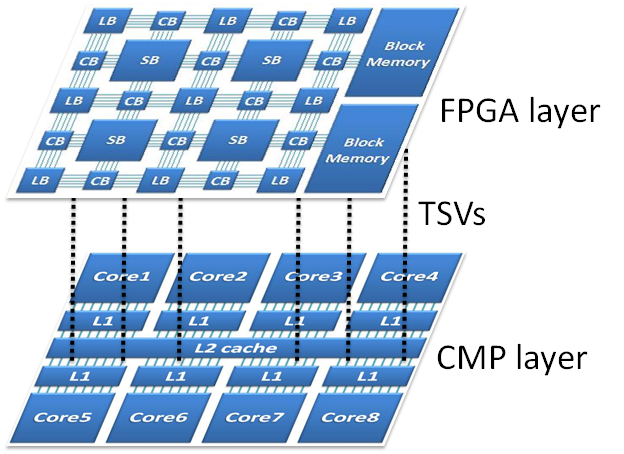

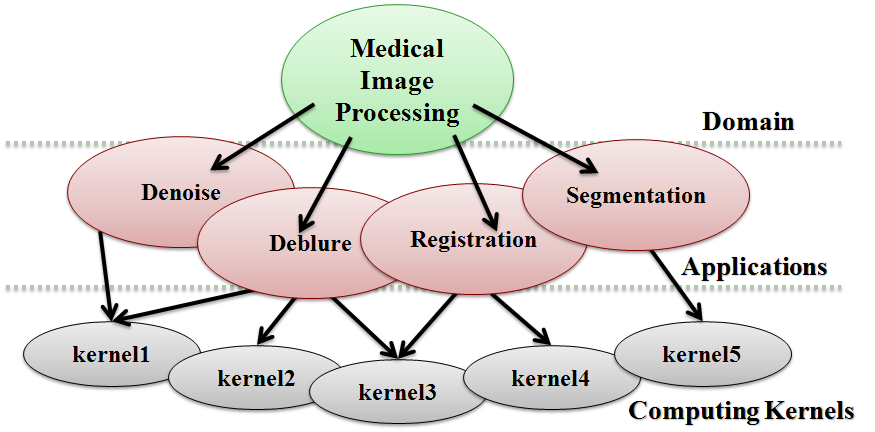

We are also exploring novel 3D architectures. We have proposed the accelerator-over-processor computing platform as shown below. The accelerators in this architecture are designed for a specific domain. They can be shared among applications in the domain. It provides an easy way to extend a general-purpose processor to a domain-specific professor with significant performance improvement and energy savings. We also developed optimization methodologies to maximize the gain under any given area/bandwidth constraints.

For software download and more details: here